- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

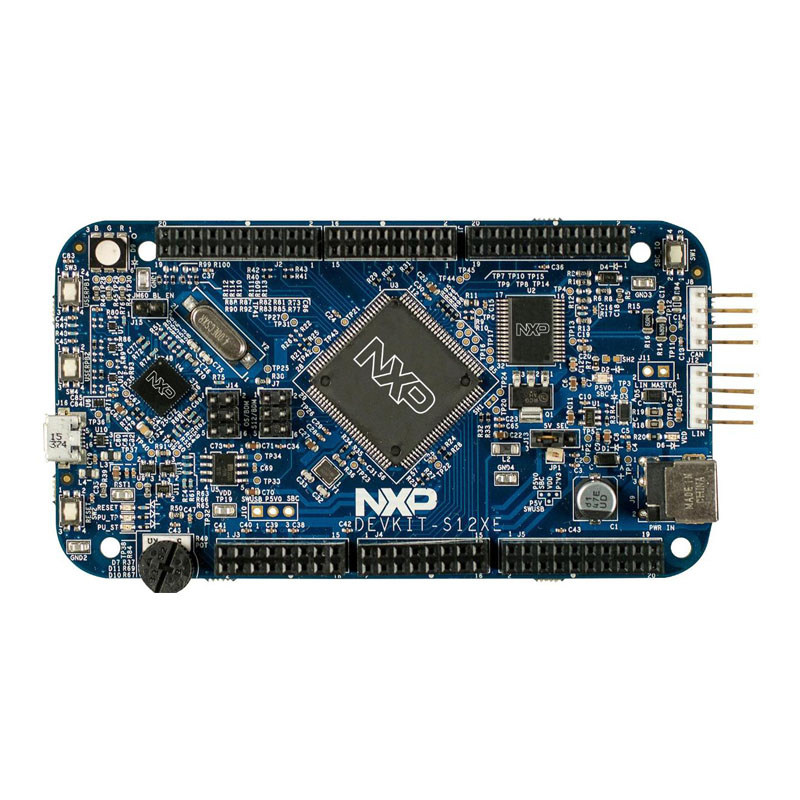

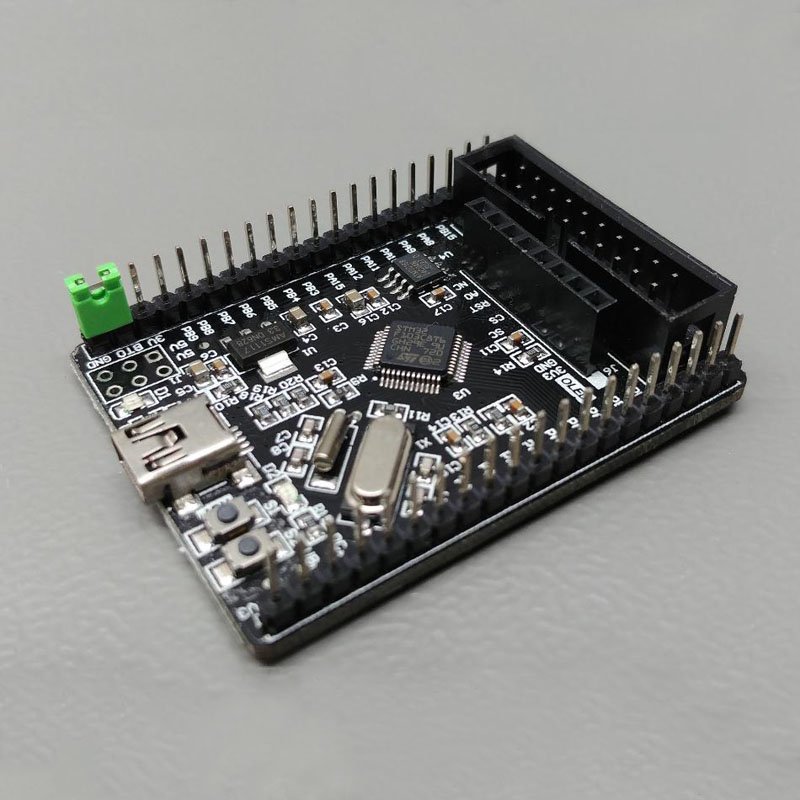

ARM STM32 MCU-kort

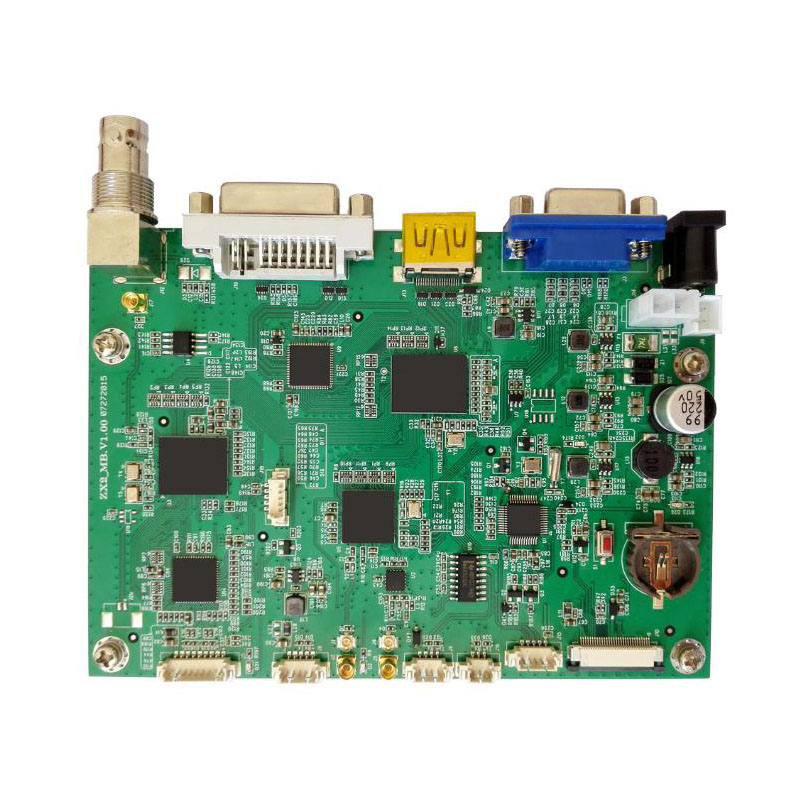

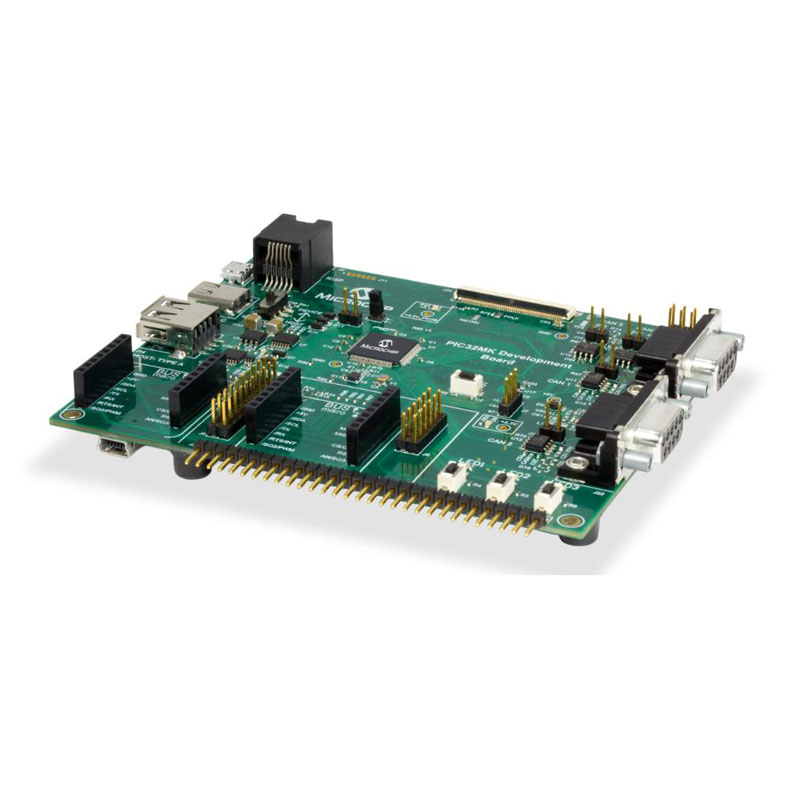

Ningbo Hi-tech Easy Choice Technology Co., Ltd er en højteknologisk virksomhed, der er aktiv i design, udvikling og produktion af ARM STM32 MCU Board. Vores virksomheds omdømme er bygget på god kredit og yder enestående service, hvilket har resulteret i langsigtede samarbejder med betydelige virksomheder, offentlige myndigheder og et bredt brugerfællesskab. Vi specialiserer os i udvikling af intelligent elektronisk styrekort, mekanisk og elektrisk kontrolproduktdesign single-chip mikrocomputerudvikling, kredsløbsdesign og post-produktionstest. Vi kan specialdesigne styrekredsløbet til at tilfredsstille dine behov, hvilket muliggør opfyldelse af dine tilsigtede produktfunktioner, uanset om du leverer eksplicitte funktionskrav eller blot en idé.

Send forespørgsel

YCTECH industrielt produktkontrolkortudvikling omfatter industrielt styrekortsoftwaredesign, softwareopgradering, skematisk diagramdesign, PCB-design, PCB-produktion og PCBA-behandling placeret i Kinas østkyst. Vores virksomhed designer, udvikler og producerer ARM STM32 MCU-kort. Kerne: ARM32-bit Cortex-M3 CPU, den højeste driftsfrekvens er 72MHz, 1,25DMIPS/MHz. Single-cycle multiplikation og hardware divide.

Hukommelse: On-chip integreret 32-512KB Flash-hukommelse. 6-64KB SRAM-hukommelse.

Ur, nulstilling og strømstyring: 2,0-3,6V strømforsyning og drivspænding til I/O-interface. Power-on reset (POR), power-down reset (PDR) og programmerbar spændingsdetektor (PVD). 4-16MHz krystaloscillator. Indbygget 8MHz RC-oscillatorkredsløb justeret før fabrik. Internt 40 kHz RC oscillatorkredsløb. PLL for CPU ur. 32kHz krystal med kalibrering til RTC.

Lavt strømforbrug: 3 tilstande med lavt strømforbrug: dvale, stop, standby. VBAT til at forsyne RTC og backup registre.

Debug mode: seriel debug (SWD) og JTAG-grænseflade.

DMA: 12-kanals DMA-controller. Understøttede ydre enheder: timere, ADC, DAC, SPI, IIC og UART.

Tre 12-bit us-niveau A/D-konvertere (16 kanaler): A/D-måleområde: 0-3,6V. Mulighed for dobbelt prøve og hold. En temperatursensor er integreret på chip.

2-kanals 12-bit D/A-konverter: STM32F103xC, STM32F103xD, STM32F103xE eksklusiv.

Op til 112 hurtige I/O-porte: Afhængigt af modellen er der 26, 37, 51, 80 og 112 I/O-porte, som alle kan tilknyttes 16 eksterne interrupt-vektorer. Alle undtagen de analoge indgange kan acceptere indgange op til 5V.

Op til 11 timere: 4 16-bit timere, hver med 4 IC/OC/PWM eller pulstællere. To 16-bit 6-kanals avancerede kontroltimere: op til 6 kanaler kan bruges til PWM-output. 2 vagthund timere (uafhængig vagthund og vindue vagthund). Systick-timer: 24-bit nedtæller. To 16-bit grundlæggende timere bruges til at drive DAC'en.

Op til 13 kommunikationsgrænseflader: 2 IIC-grænseflader (SMBus/PMBus). 5 USART-grænseflader (ISO7816-grænseflade, LIN, IrDA-kompatibel, debug-kontrol). 3 SPI interfaces (18 Mbit/s), hvoraf to er multiplekset med IIS. CAN interface (2.0B). USB 2.0 fuld hastighed interface. SDIO interface.

ECOPACK-pakke: STM32F103xx-seriens mikrocontrollere anvender ECOPACK-pakken.

system effekt

1. ARM Cortex-M3-kerne integreret med indlejret Flash og SRAM-hukommelse. Sammenlignet med 8/16-bit-enheder giver ARM Cortex-M3 32-bit RISC-processor højere kodeeffektivitet. STM32F103xx mikrocontrollere har en indlejret ARM-kerne, så de er kompatible med alle ARM-værktøjer og -software.

2. Embedded Flash-hukommelse og RAM-hukommelse: Indbygget op til 512KB indlejret Flash, som kan bruges til at gemme programmer og data. Op til 64KB indlejret SRAM kan læses og skrives ved CPU-clockhastighed (ingen ventetilstande).

3. Variabel statisk hukommelse (FSMC): FSMC er indlejret i STM32F103xC, STM32F103xD, STM32F103xE, med 4 chipvalg og understøtter fire tilstande: Flash, RAM, PSRAM, NOR og NAND. 3 FSMC afbrydelseslinjer er forbundet til NVIC efter OR. Der er ingen læse/skrive-FIFO, bortset fra PCCARD, koder udføres fra ekstern hukommelse, Boot understøttes ikke, og målfrekvensen er lig med SYSCLK/2, så når systemuret er 72MHz, udføres ekstern adgang ved 36MHz.

4. Nested Vectored Interrupt Controller (NVIC): Den kan håndtere 43 maskerbare interrupt-kanaler (eksklusive 16 interrupt-linjer i Cortex-M3), hvilket giver 16 interrupt-prioriteter. Tæt koblet NVIC opnår lavere interrupt-behandlingsforsinkelse, overfører direkte interrupt-entry-vektortabeladressen til kernen, tæt koblet NVIC-kernegrænseflade, tillader afbrydelser at blive behandlet på forhånd, håndterer afbrydelser med højere prioritet, der ankommer senere, og understøtter tail Chain, gemmer automatisk processortilstanden, og afbrydelsesindtastningen gendannes automatisk, når afbrydelsen afsluttes, uden instruktionsintervention.

5. Ekstern afbrydelses-/hændelsescontroller (EXTI): Den eksterne afbrydelses-/hændelsescontroller består af 19 kantdetektorlinjer til generering af afbrydelses-/hændelsesanmodninger. Hver linje kan konfigureres individuelt til at vælge triggerhændelsen (stigende kant, faldende kant eller begge dele) og kan maskeres individuelt. Der er et afventende register til at opretholde status for afbrydelsesanmodninger. EXTI er i stand til at detektere, når en puls på den eksterne linje er længere end perioden for det interne APB2-ur. Op til 112 GPIO'er er forbundet til 16 eksterne afbrydelseslinjer.

6. Ur og start: Det er stadig nødvendigt at vælge systemuret ved start, men den interne 8MHz krystaloscillator vælges som CPU-ur ved nulstilling. Et eksternt 4-16MHz ur kan vælges og vil blive overvåget for succes. I løbet af denne tid er controlleren deaktiveret, og softwareafbrydelsesstyring deaktiveres efterfølgende. Samtidig er afbrydelsesstyring af PLL-uret fuldt tilgængelig, hvis det kræves (f.eks. i tilfælde af fejl på en indirekte brugt krystaloscillator). Flere præ-komparatorer kan bruges til at konfigurere AHB-frekvensen, herunder højhastigheds-APB (PB2) og lavhastigheds-APB (APB1). Den højeste frekvens for højhastigheds-APB er 72MHz, og den højeste frekvens for lavhastigheds-APB er 36MHz.

7. Boot mode: Ved opstart bruges Boot pin til at vælge en af de tre Boot muligheder: import fra bruger Flash, import fra systemhukommelse og import fra SRAM. Boot-importprogrammet er placeret i systemhukommelsen og bruges til at omprogrammere Flash-hukommelsen gennem USART1.

8. Strømforsyningsskema: VDD, spændingsområdet er 2,0V-3,6V, den eksterne strømforsyning leveres gennem VDD-stiften, som bruges til I/O og intern spændingsregulator. VSSA og VDDA, spændingsområdet er 2,0-3,6V, ekstern analog spændingsindgang til ADC, nulstillingsmodul, RC og PLL, inden for området for VDD (ADC er begrænset til 2,4V), VSSA og VDDA skal tilsluttes VSS i overensstemmelse hermed og VDD. VBAT, spændingsområdet er 1,8-3,6V, når VDD er ugyldigt, leverer det strøm til RTC, ekstern 32KHz krystaloscillator og backup registre (realiseret ved strømskift).

9. Strømstyring: Enheden har et komplet power-on reset (POR) og power-down reset (PDR) kredsløb. Dette kredsløb er altid effektivt til at sikre, at nogle nødvendige operationer udføres, når man starter fra 2V eller falder til 2V. Når VDD er under en specifik nedre grænse VPOR/PDR, kan enheden også forblive i nulstillingstilstand uden et eksternt nulstillingskredsløb. Enheden har en indbygget programmerbar spændingsdetektor (PVD). PVD'en bruges til at detektere VDD og sammenligne den med VPVD-grænsen. Et interrupt genereres, når VDD er lavere end VPVD eller VDD er større end VPVD. Afbrydelsesservicerutinen kan generere en advarselsmeddelelse eller placere MCU'en i en sikker tilstand. PVD er aktiveret af software.

10. Spændingsregulering: Spændingsregulatoren har 3 driftstilstande: hoved (MR), lavt strømforbrug (LPR) og power down. MR bruges i reguleringstilstand (running mode) i traditionel forstand, LPR bruges i stop mode, og power-down bruges i standby mode: Spændingsregulatorens udgang er højimpedans, kernekredsløbet er slukket, inkl. nul forbrug (indholdet af registre og SRAM er ikke vil gå tabt).

11. Lavt strømforbrugstilstand: STM32F103xx understøtter 3 lavt strømforbrugstilstande, for at opnå den bedste balance mellem lavt strømforbrug, kort opstartstid og tilgængelige vækningskilder. Dvaletilstand: kun CPU'en holder op med at fungere, alle perifere enheder fortsætter med at køre, vækk CPU'en, når der opstår en afbrydelse/begivenhed; stoptilstand: gør det muligt at vedligeholde indholdet af SRAM og registre med minimalt strømforbrug. Urene i 1,8V-regionen er alle stoppet, PLL-, HSI- og HSE RC-oscillatorerne er deaktiveret, og spændingsregulatoren er placeret i normal eller laveffekttilstand. Enheden kan vækkes fra stop-tilstand via en ekstern afbrydelseslinje. Den eksterne afbrydelseskilde kan være en af 16 eksterne afbrydelseslinjer, PVD-udgang eller TRC-advarsel. Standby-tilstand: I jagten på det mindste strømforbrug slukkes den interne spændingsregulator, så 1,8V-området slukkes. PLL, HSI og HSE RC oscillatorer er også deaktiveret. Efter at have gået i standby-tilstand, ud over backup-registre og standby-kredsløb, går indholdet af SRAM og registre også tabt. Enheden afslutter standbytilstand, når ekstern nulstilling (NRST-pin), IWDG-nulstilling, stigende kant på WKUP-ben eller TRC-advarsel forekommer. Når du går ind i stoptilstand eller standbytilstand, vil TRC, IWDG og relaterede urkilder ikke blive stoppet.